2008年01月05日

■ 四半世紀越しの「de BUG」

━━━━━━━━━━━━● de BUG ●━━━━━━━━━━━━

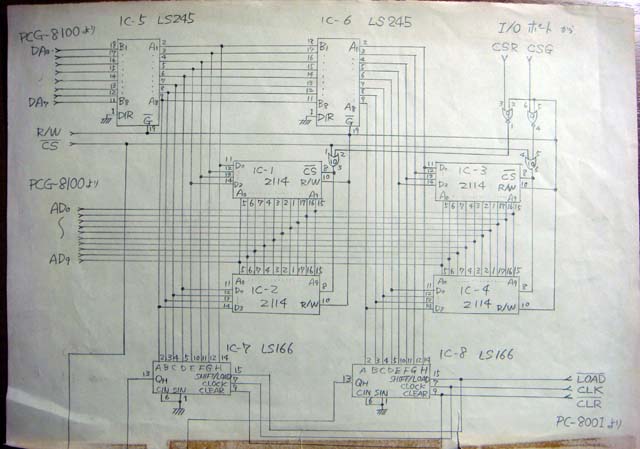

I/O'83年12月号の“PCGをフルドット・カラーに”の回路図に誤りがありました。

- 図1の右端中央部の「LOAD CLR CLK」は「LOAD CLK CLR」の誤りです。(重要)

- その下の「WB WB WG1 WG2」は「WB WR WG1 WG2」の誤りです。

- その下の「DB DR (空白)」は「DB DR DG」の誤りです。

- 図1の左下にあるIC9のNORゲートにピン番号が欠けていました。入力が11、12、出力が13です。

- その右のIC10のORゲートのピン番号も欠けていました。入力が10、9、出力が8です。

- 図1上部のIC2とIC4の8番ピンの名前が欠けていました。これは「CS」です。

また、図1の上部左端の「PCG-8100より」の「AD0〜AD9」の並び順が、接続先のIC 2114の「A0〜A9」の並び順と逆になっていますが、これはこのままでも問題ありません。スタティックRAMですのでアドレスの上位下位に関係なく動作します。筆者もなぜかこの順で製作してしまいましたが、正常に動作しました。

2008年1月5日

ずっと胸の奥に刺さっていた誤りを今更ながら訂正。このバグに気付いたのは、記事が掲載されてから何年も経ったある日のこと。I/O編集部から封書が送られてきた。封筒を開けると読者からの励ましのお便りが何通か入っていて、その1つに、アドレスバスの並び順が違うのではないかという質問があった。なぜ今頃になって転送されて来たのだ?と疑問に思いつつ確かめてみると、たしかにその通り。ただ、そこは逆順でもかまわないということで、お返事の手紙を書いたのを覚えている。その際、記事を久しぶりに見て、何か所かの誤植に気付いた。

特に致命的だったのが、上に書いた1つ目の、「CLR」と「CLK」が逆になっているところ。繋がっている先のIC8が「CLOCK」と「CLEAR」になっていることから気付く読者もあったとは思うが、書かれている通りに製作する読者は気付かなかったかもしれない。「作ってみたけど動かなかった」ということは容易に起こり得た話で、もっと早く気付いて編集部に伝え「de BUG」に乗せてもらうべきだった。気付いたときには既に4、5年?も経っていて、今から作る人はさすがにいないだろうということで、そのままにしてしまった。まことに申し訳ない。以下が投稿時の原稿で、原稿では正しい。

ちなみに、この回路は後から思えば下手糞な設計だった。

まず、PCGからのデータバスが、74LS245 (3-State Octal Bus Transceivers) を通して2114 (4K nMOS Static RAM) に供給されているわけだが、なぜ IC5 を通したものをさらに IC6 に通すのかという疑問がわく。普通なら、PCGからのデータバスを直接2つの74LS245に渡して、それぞれを2114に供給するだろう。たぶん、配線レイアウトを先に考えて、引き回しが楽になるようにこうしたのだったと思われるが、遅延が増えるとか、そういう発想が皆無だった。なお、74LS245じゃなくて74LS241 (Octal Buffers and Line Drivers With 3-State Outputs)で十分なのでは?という話もあるが、これも配線の方向を揃えたくてあえてこうしたのだった。

このころはタイミングというものをまるで理解していなかった。信号は瞬時にHからLへ、LからHへ変化するものというデジタル思考でしか理解しておらず、規格表や設計図にある台形状の波形図を見ていたはずなのに、線が斜めになっていることの意味をまるでわかっていなかった。そのため、実際、次の問題が生じた。

記事中のリスト2に「カラーパレット・プログラム例」が次のように載っている。

1000 OUT &H92, 3 1010 OUT &H91, (C1 AND 3) + C2 * 4 1020 OUT &H92, 2 + ((C1 AND 4) <> 0) 1030 OUT &H92, 3 1040 RETURN

なぜこんなに煩雑なのか。じつは最初は、たしか次のような感じに書いていた。

1000 OUT &H92, 2 + ((C1 AND 4) <> 0) 1010 OUT &H91, (C1 AND 3) + C2 * 4 1020 RETURN

これでは思ったように動作しなかった。指定したのとは違う色のパレットの値が置き換わってしまう。何度もあらゆるパターンを試していくらか法則があることを掴んだ。

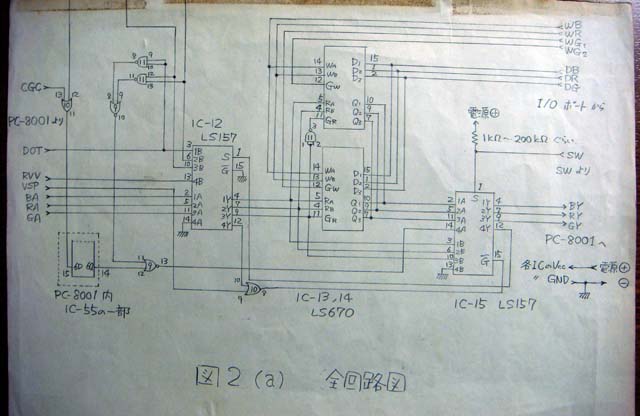

これは、回路図中の 74LS670 (4-by-4 Register Files) を制御している。74LS670は、今風に言えばデュアルポートRAMに相当するもので、読み出しアクセス中に別のポートからアドレス(といっても2ビットしかないが)を指定して書き込みができるというもの。書き換えたいチップ(IC13またはIC14)をGWで指定(OUT &H92)した後に、アドレスに当たるWAとWB、データであるDB、DR、DGを出力(OUT &H91)すればうまくいくだろうと思っていた。しかし、それで何が起きたかというと、OUT &H91でWA、WB、DB、DR、DGを変更した瞬間、WA、WBが確定しない間に DB、DR、DGが変化するものだから、前の状態のWA、WBで指定されていたビットも書き換わってしまうことがあるという現象だった。

この時はじめて、波形図が台形で斜め線で描かれていることの意味を理解したのだった。原因がわかったところで、一旦GWをネゲートした上でアドレスとデータを出力し、必要なGWのアサートをして再びネゲートするという制御をOUTポートで行うという方法で解決したのが、リスト2のコードだ。

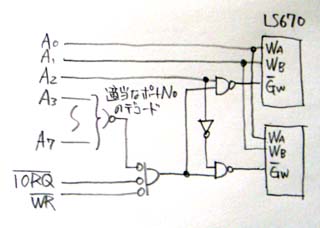

後から思えば、そもそも、8255 (Programmable Peripheral Interface) なんか使わずに、直接CPUのデータバスの下位3ビットを DB、DR、DGにつなぎ、アドレスバスの下位3ビットを WA、WB、GWにつないで、GWにゲートを挟んで、CPUが出力するIORQとWR信号で制御してやればよかったのだ。

(今書いた手書き)

つまり、74LS670を、I/Oポートを実現するラッチと見なして設計すればよかった。当時はCPUのバス制御の仕組みを理解しておらず、I/Oポートは「8255で作るもの」と思い込んでいて、I/Oをブラックボックスとして理解していたため、そこに思い至らなかった。8255を通して制御する必然性は全くなかった。このことに気付いたのはしばらくした後で、1986年7月号の「640×400ドット フルドット・カラーグラフィック」(PC-8801初代機の改造)ではこの反省を踏まえた。

このようにしていれば、プログラムからの制御は、I/Oポートを例えば 90 〜 97 に割り当てたなら、単純に次のようにできた。(たしか、PC-8801のカラーパレットもこんな感じではなかったかと。)

1000 OUT &H90 + (C1 AND 7), C2 1010 RETURN

そんなこともあって、これを実際に作った方がいらっしゃると知ったときはちょっと恥ずかしかった。ある程度内容を把握しないと製作できない代物だったわけで、内容の分かる方には「ダサい設計だなこりゃ」と思われていたかもしれない。

ちなみに、フルドットカラーにする部分については、独立に同様の方法で製作なさった方がいらしたようで、以前、http://www.sofarts.com/computer/env-hard/history/pc-8001/p5.htm のURLのページにそのことが書かれていた。今は消えているようだ。たしか、対応ソフトをいくつか書かれたとのことで、エミュレータに対応を期待する声が書かれていた。

対応ソフトは他に、当時誌上発表されたものとして、I/O 1985年4月号に掲載されたPCGキャラクタエディタがある。当時、製作された方がいらしたと知って大感激だった。

私もいくつか対応ソフトを作ったのだが、まだデータを吸い出せていない。肝心なフロッピーディスクが見あたらない。捨てるということはないはずなので、どこかにあるはず。正月休みはもう終わり。続きは夏休みだ。